Orders Over

$5000Intel EPM7256BTC144-7N

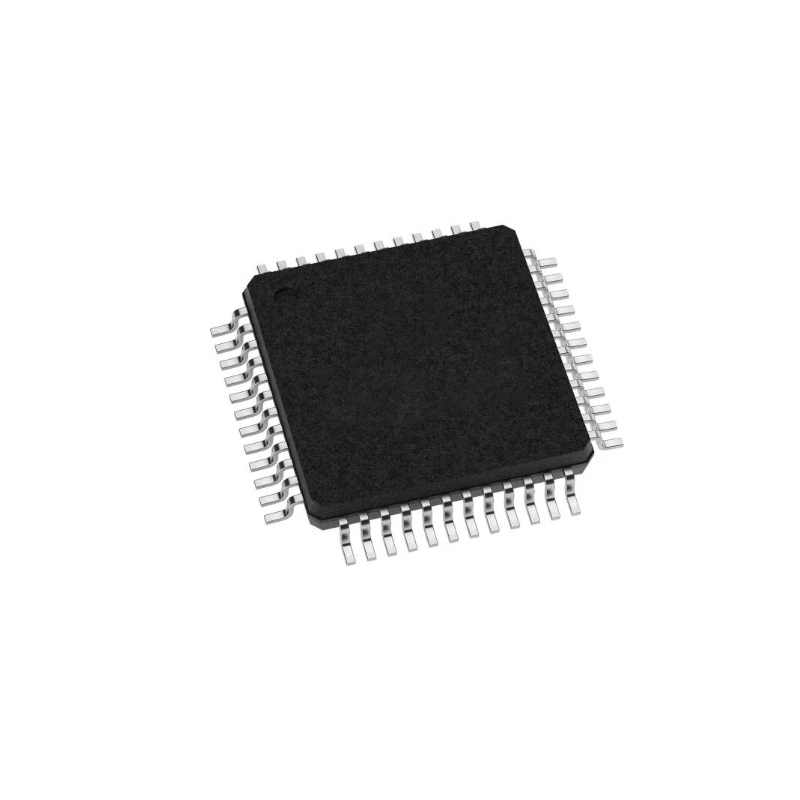

CPLD MAX® 7000B Family 5K Gates 256 Macro Cells 126.6MHz 2.5V 144-Pin TQFP Tray

Brands: Intel

Mfr.Part #: EPM7256BTC144-7N

Datasheet: EPM7256BTC144-7N Datasheet (PDF)

Package/Case: TQFP-44

Product Type: CPLDs (Complex Programmable Logic Devices)

RoHS Status:

Stock Condition: 9,458 pcs, New Original

Warranty: 1 Year Ovaga Warranty - Find Out More

0

1

Features

- High-performance 2.5-V CMOS EEPROM-based programmable logic devices (PLDs) built on second-generation Multiple Array MatriX (MAX®) architecture (see Table 1)

- – Pin-compatible with the popular 5.0-V MAX 7000S and 3.3-V MAX 7000A device families

- – High-density PLDs ranging from 600 to 10,000 usable gates

- – 3.5-ns pin-to-pin logic delays with counter frequencies in excess of 303.0 MHz

- Advanced 2.5-V in-system programmability (ISP)

- – Programs through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface with advanced pin-locking capability

- – Enhanced ISP algorithm for faster programming

- – ISP_Done bit to ensure complete programming

- – Pull-up resistor on I/O pinsduring in-system programming

- – ISP circuitry compliant with IEEE Std. 1532

- System-level features

- –MultiVoltTM I/O interface enabling device core to run at 2.5 V, while I/O pins are compatible with3.3-V, 2.5-V, and 1.8-V logic levels

- – Programmable power-saving mode for 50%or greater power reduction in each macrocell

- – Fast input setup times provided by a dedicated path from I/O pin to macrocell registers

- – Support for advanced I/O standards, including SSTL-2 and SSTL-3, and GTL+

- – Bus-hold option on I/O pins

- – PCI compatible

- – Bus-friendly architecture including programmable slew-rate control

- – Open-drain output option

- – Programmable security bit for protection of proprietary designs

- – Built-in boundary-scan testcircuitry compliant with IEEE Std. 1149.1

- – Supports hot-socketing operation

- – Programmable ground pins

- Advanced architecture features

- – Programmable interconnect array (PIA) continuous routing structure for fast, predictable performance

- – Configurable expander product-term distribution, allowing up to 32 product terms per macrocell

- – Programmable macrocell registers with individual clear, preset, clock, and clock enable controls

- – Two global clock signals with optional inversion

- – Programmable power-up states for macrocell registers

- – 6 to 10 pin- or logic-driven output enable signals

- Advanced package options

- – Pin counts ranging from 44 to 256 ina variety of thin quad flat pack (TQFP), plastic quad flatpack (PQFP), ball-grid array (BGA), space-saving FineLine BGATM, 0.8-mm Ultra FineLine BGA, and plastic J-lead chip carrier (PLCC) packages

- – Pin-compatibility with other MAX 7000B devices in the same package

- Advanced software support

- – Software design support and automatic place-and-route provided by Altera’s MAX+PLUS® II development system for Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations

- – Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPMs), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, and VeriBest

- – Programming support with Altera’s Master Programming Unit (MPU), MasterBlasterTM serial/universal serial bus (USB) communications cable, and ByteBlasterMVTM parallel port download cable, as well as programming hardware from third party manufacturers and any JamTM STAPL File (.jam), Jam Byte Code File (.jbc), or Serial Vector Format File (.svf)-capable in circuit tester

Specifications

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| Manufacturer: | Intel | Product Category: | CPLD - Complex Programmable Logic Devices |

| RoHS: | Details | Series: | EPM7256B |

| Mounting Style: | SMD/SMT | Package / Case: | TQFP-44 |

| Operating Supply Voltage: | 2.5 V | Number of Macrocells: | 256 |

| Number of I/Os: | 36 I/O | Supply Voltage - Max: | 3.6 V |

| Supply Voltage - Min: | 3 V | Minimum Operating Temperature: | 0 C |

| Maximum Operating Temperature: | + 70 C | Maximum Operating Frequency: | 188.7 MHz |

| Propagation Delay - Max: | 5 ns | Packaging: | Tray |

| Brand: | Intel / Altera | Memory Type: | EEPROM |

| Moisture Sensitive: | Yes | Number of Gates: | 5000 |

| Number of Logic Array Blocks - LABs: | 16 | Product Type: | CPLD - Complex Programmable Logic Devices |

| Factory Pack Quantity: | 60 | Subcategory: | Programmable Logic ICs |

| Tradename: | MAX 7000 |

Shipping

| Shipping Type | Ship Fee | Lead Time | |

|---|---|---|---|

|

DHL | $20.00-$40.00 (0.50 KG) | 2-5 days |

|

Fedex | $20.00-$40.00 (0.50 KG) | 2-5 days |

|

UPS | $20.00-$40.00 (0.50 KG) | 2-5 days |

|

TNT | $20.00-$40.00 (0.50 KG) | 2-5 days |

|

EMS | $20.00-$40.00 (0.50 KG) | 2-5 days |

|

REGISTERED AIR MAIL | $20.00-$40.00 (0.50 KG) | 2-5 days |

Processing Time:Shipping fee depend on different zone and country.

Payment

| Terms of payment | Hand Fee | |

|---|---|---|

|

Wire Transfer | charge US$30.00 banking fee. |

|

Paypal | charge 4.0% service fee. |

|

Credit Card | charge 3.5% service fee. |

|

Western Union | charge US.00 banking fee. |

|

Money Gram | charge US$0.00 banking fee. |

Guarantees

1.The electronic components you purchase include 365 Days Warranty, We guarantee product quality.

2.If some of the items you received aren't of perfect quality, we would resiponsibly arrange your refund or replacement. But the items must remain their orginal condition.

Packing

-

![Product Product]()

Step1 :Product

-

![Vacuum packaging Vacuum packaging]()

Step2 :Vacuum packaging

-

![Anti-static bag Anti-static bag]()

Step3 :Anti-static bag

-

![Individual packaging Individual packaging]()

Step4 :Individual packaging

-

![Packaging boxes Packaging boxes]()

Step5 :Packaging boxes

-

![bar-code shipping tag bar-code shipping tag]()

Step6 :bar-code shipping tag

All the products will packing in anti-staticbag. Ship with ESD antistatic protection.

Outside ESD packing’s lable will use ourcompany’s information: Part Mumber, Brand and Quantity.

We will inspect all the goods before shipment,ensure all the products at good condition and ensure the parts are new originalmatch datasheet.

After all the goods are ensure no problems afterpacking, we will packing safely and send by global express. It exhibitsexcellent puncture and tear resistance along with good seal integrity.

We provide high quality products, thoughtful service and after sale guarantee

-

![Product Product]()

We have rich products, can meet your various needs.

-

![quantity quantity]()

Minimum order quantity starts from 1pcs.

-

![shipping shipping]()

Lowest international shipping fee starts from $0.00

-

![guarantee guarantee]()

365 days quality guarantee for all products