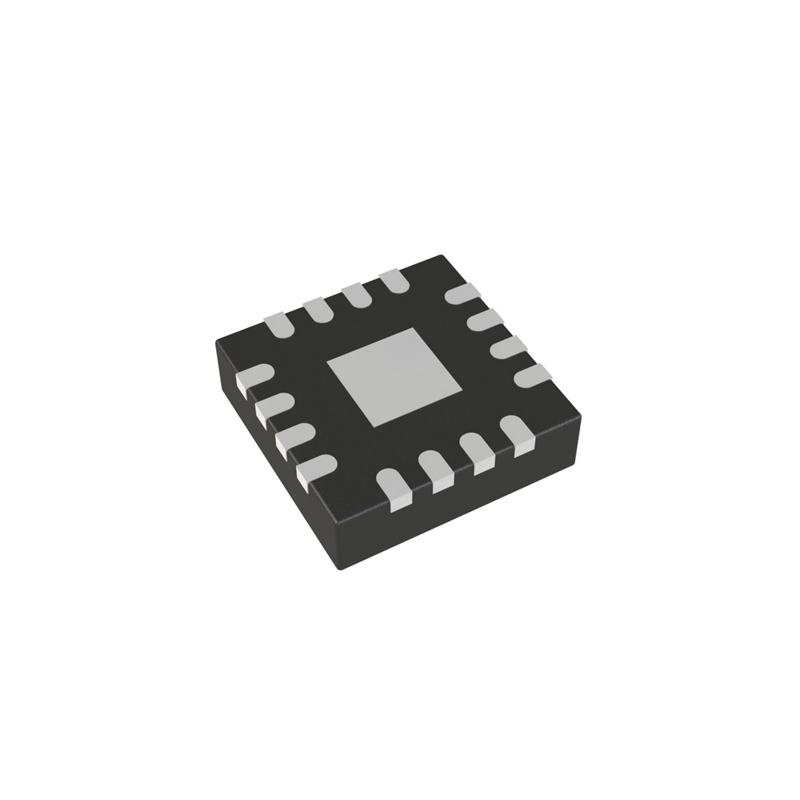

Renesas 1894K-32LFT

Ethernet ICs 3.3V 10/100 PHY RMII

Brands: Renesas Technology Corp

Mfr.Part #: 1894K-32LFT

Datasheet: 1894K-32LFT Datasheet (PDF)

Package/Case: 32-VFQFN

RoHS Status:

Stock Condition: 3211 pcs, New Original

Product Type: Interface ICs

Warranty: 1 Year Ovaga Warranty - Find Out More

0

1

*All prices are in USD

| Qty | Unit Price | Ext Price |

|---|---|---|

| 1 | $4.717 | $4.717 |

| 200 | $1.826 | $365.200 |

| 500 | $1.762 | $881.000 |

| 1000 | $1.731 | $1731.000 |

In Stock:3211 PCS

1894K-32LFT General Description

The IDT1894-32 is a low-power, physical-layer device (PHY) that supports the ISO/IEC 10Base-T and 100Base-TX Carrier-Sense Multiple Access/Collision Detection (CSMA/CD) Ethernet standards, ISO/IEC 8802-3. The IDT1894-32 is intended for MII, Node applications that require the Auto-MDIX feature that automatically corrects crossover errors in plant wiring. The IDT1894-32 incorporates Digital-Signal Processing (DSP) control in its Physical-Medium Dependent (PMD) sub layer. As a result, it can transmit and receive data on unshielded twisted-pair (UTP) category 5 cables with attenuation in excess of 24 dB at 100MHz. With this IDT-patented technology, the IDT1894-32 can virtually eliminate errors from killer packets. The IDT1894-32 provides a Serial-Management Interface for exchanging command and status information with a Station-Management (STA) entity. The IDT1894-32 Media-Dependent Interface (MDI) can be configured to provide either half- or full duplex operation at data rates of 10 Mb/s or 100Mb/s. In addition, the IDT1894-32 includes a programmable interrupt output function. This function consists of a digital output pin, an interrupt control register, a set of interrupt status register bits and a corresponding set of interrupt enable bits, and a pre-defined set of events which can be assigned as one of the interrupt sources. The purpose of this function is to notify the host of this PHY device when certain event happens via interrupt (the logic level on interrupt output pin going low or going high) instead of polling by the host. The events that could be used to generate interrupts are: receiver error, Jabber, page received, parallel detect fault, link partner acknowledge, link status change, auto-negotiation complete, remote fault, collision, etc. Applications: NIC cards, PC motherboards, switches, routers, DSL and cable modems, game machines, printers, network connected appliances, and industrial equipment.

Features

- Supports category 5 cables with attenuation in excess of 24dB at 100 MHz.

- Single-chip, fully integrated PHY provides PCS, PMA, PMD, and AUTONEG sub layers functions of IEEE standard.

- 10Base-T and 100Base-TX IEEE 8802.3 compliant

- MIIM (MDC/MDIO) management bus for PHY register configuration

- RMII interface support with external 50 MHz system clock

- Single 3.3V power supply

- Highly configurable

- Media Independent Interface (MII)

- Auto-Negotiation with Parallel detection

- Node applications, managed or unmanaged

- 10M or 100M full and half-duplex modes

- Loopback mode for Diagnostic FunctionsAuto-MDI/MDIX crossover correction

- Low-power CMOS (typically 300 mW)

- Power-Down mode typically 21mW

- Clock and crystal supported

- Interrupt pin option

- Fully integrated, DSP-based PMDAdaptive equalization and baseline-wander correction

- Transmit wave shaping and stream cipher scrambler

- MLT-3 encoder and NRZ/NRZI encoder

- Single power supply (3.3 V)

- Built-in 1.8 V regulator for core

- Available in 32-pin (5mm x 5mm) QFN package, Pb-free

- Available in Industrial Temp and Lead Free

Specifications

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| Pin Count | 33 | Package Category | Quad Flat No-Lead |

| Released Date | Jan 28, 2020 | Last Modified Date | Aug 1, 2023 1:40 PM UTC |

| Series | PHYceiver™ | Product Status | Active |

| Programmabe | Not Verified | Protocol | Ethernet |

| Function | Physical Layer Controller | Interface | Parallel |

| Standards | 10/100 Base-T/TX PHY | Voltage - Supply | 3.14V ~ 3.47V |

| Operating Temperature | 0°C ~ 70°C | Package / Case | 32-VFQFN Exposed Pad |

| Supplier Device Package | 32-VFQFPN (5x5) |

Shipping

| Shipping Type | Ship Fee | Lead Time | |

|---|---|---|---|

|

DHL | $20.00-$40.00 (0.50 KG) | 2-5 days |

|

Fedex | $20.00-$40.00 (0.50 KG) | 2-5 days |

|

UPS | $20.00-$40.00 (0.50 KG) | 2-5 days |

|

TNT | $20.00-$40.00 (0.50 KG) | 2-5 days |

|

EMS | $20.00-$40.00 (0.50 KG) | 2-5 days |

|

REGISTERED AIR MAIL | $20.00-$40.00 (0.50 KG) | 2-5 days |

Processing Time:Shipping fee depend on different zone and country.

Payment

| Terms of payment | Hand Fee | |

|---|---|---|

|

Wire Transfer | charge US$30.00 banking fee. |

|

Paypal | charge 4.0% service fee. |

|

Credit Card | charge 3.5% service fee. |

|

Western Union | charge US.00 banking fee. |

|

Money Gram | charge US$0.00 banking fee. |

Guarantees

1.The electronic components you purchase include 365 Days Warranty, We guarantee product quality.

2.If some of the items you received aren't of perfect quality, we would resiponsibly arrange your refund or replacement. But the items must remain their orginal condition.

Packing

-

![Product Product]()

Step1 :Product

-

![Vacuum packaging Vacuum packaging]()

Step2 :Vacuum packaging

-

![Anti-static bag Anti-static bag]()

Step3 :Anti-static bag

-

![Individual packaging Individual packaging]()

Step4 :Individual packaging

-

![Packaging boxes Packaging boxes]()

Step5 :Packaging boxes

-

![bar-code shipping tag bar-code shipping tag]()

Step6 :bar-code shipping tag

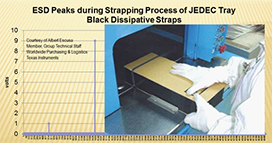

All the products will packing in anti-staticbag. Ship with ESD antistatic protection.

Outside ESD packing’s lable will use ourcompany’s information: Part Mumber, Brand and Quantity.

We will inspect all the goods before shipment,ensure all the products at good condition and ensure the parts are new originalmatch datasheet.

After all the goods are ensure no problems afterpacking, we will packing safely and send by global express. It exhibitsexcellent puncture and tear resistance along with good seal integrity.

Datasheet PDF

We provide high quality products, thoughtful service and after sale guarantee

-

![Product Product]()

We have rich products, can meet your various needs.

-

![quantity quantity]()

Minimum order quantity starts from 1pcs.

-

![shipping shipping]()

Lowest international shipping fee starts from $0.00

-

![guarantee guarantee]()

365 days quality guarantee for all products

Ovaga has reliable components that work well for my business projects.