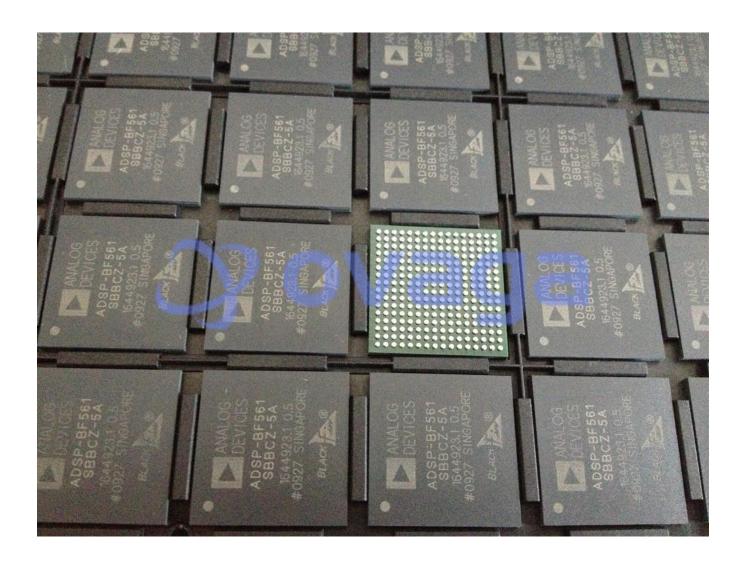

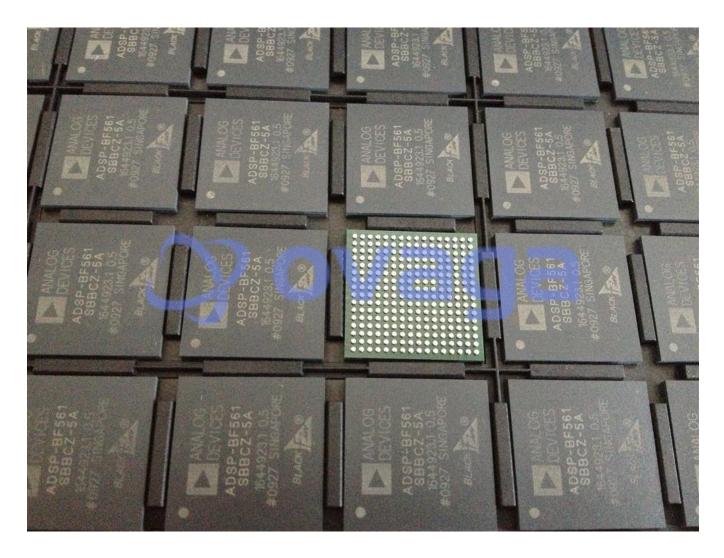

# ADSP-BF561SBBCZ-5A

Data Sheet

Analog Devices ADSP-BF561SBBCZ-5A, 32Bit Blackfin Digital Signal Processor 500MHz 16Bit ROM 256Pin BGA

Manufacturers Analog Devices, Inc

Package/Case CSPBGA-256

Product Type Embedded Processors & Controllers

RoHS Rohs

Lifecycle

Images are for reference only

Please submit RFQ for ADSP-BF561SBBCZ-5A or Email to us: sales@ovaga.com We will contact you in 12 hours.

**RFO**

### **General Description**

The Blackfin® Processor family expands the performance envelope with the ADSP-BF561. With two high performance Blackfin Processor cores, flexible cache architecture, enhanced DMA subsystem, and Dynamic Power Management (DPM) functionality, the ADSP-BF561 can support complex control and signal processing tasks while maintaining extremely high datathroughput.

The ADSP-BF561 is a functional extension of the popular Blackfin Processor family and is ideally suited for a broad range of industrial, instrumentation, medical, and consumer appliance applications—allowing for scalability based upon the required data bandwidth and mix of control, plus signal processing needed in the end product.

High-Level of Integration

328 KBytes of on-chip memory configured as:

32 KBytes of L1 instruction memory SRAM/Cache per core

64 KBytes of L1 data memory SRAM/Cache per core

4 KBytes of L1 scratchpad memory per core

128 KBytes of low-latency shared L2 memory

32-bit Memory Controller providing glueless connection to multiple banks of SDRAM, SRAM, Flash or ROM.

Two Parallel Peripheral Interfaces Units supporting ITU-R 656 video data formats.

Two dual-channel, full-duplex, synchronous serial ports supporting eight stereo I2S channels.

Dual 16 Channel DMA Controllers, supporting one and two-dimension transfers.

| SPI-compatible Port.                                                |

|---------------------------------------------------------------------|

| UART with support for IrDA®.                                        |

| 12 timer/counters supporting PWM, pulsewidth and event count modes. |

| 48 Programmable Flags/General Purpose I/O.                          |

| Event Handler.                                                      |

| Dual Watchdog timers.                                               |

| PLL capable of 1x to 63x frequency multiplication.                  |

| 256-ball Mini-BGA and 297-ball Sparse PBGA packages.                |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

|                                                                     |

#### **Features**

Dual Blackfin cores with each core capable of 600 MHz/1200 MMACs (2400 MMACs total) for demanding signal processing applications.

Large On-Chip Memory of 328 KBytes – arranged as individual L1 memory systems for each core plus a shared L2 memory space.

High data throughput tailored for the needs of imaging and consumer multimedia applications.

Application Tuned Peripherals provide glueless connectivity to a variety of audio/video converters and general-purpose ADCs/DACs.

## **Application**

328 KBytes of on-chip memory configured as:

32 KBytes of L1 instruction memory SRAM/Cache per core

64 KBytes of L1 data memory SRAM/Cache per core

4 KBytes of L1 scratchpad memory per core

128 KBytes of low-latency shared L2 memory

32-bit Memory Controller providing glueless connection to multiple banks of SDRAM, SRAM, Flash or ROM.

Two Parallel Peripheral Interfaces Units supporting ITU-R 656 video data formats.

Two dual-channel, full-duplex, synchronous serial ports supporting eight stereo I2S channels.

Dual 16 Channel DMA Controllers, supporting one and twodimension transfers.

SPI-compatible Port.

UART with support for IrDA

12 timer/counters supporting PWM, pulsewidth and event count modes.

48 Programmable Flags/General Purpose I/O.

Event Handler.

Dual Watchdog timers.

PLL capable of 1x to 63x frequency multiplication.

256-ball Mini-BGA and 297-ball Sparse PBGA packages.

32 KBytes of L1 instruction memory SRAM/Cache per core

64 KBytes of L1 data memory SRAM/Cache per core

4 KBytes of L1 scratchpad memory per core

128 KBytes of low-latency shared L2 memory

### **Related Products**

ADUC7022BCPZ62

Analog Devices, Inc LFCSP-40

ADUC841BSZ62-5

Analog Devices, Inc QFP-52

ADUC831BSZ

Analog Devices, Inc QFP-52

ADSP-21369BBPZ-2A

Analog Devices, Inc SBGA-256

ADUC7020BCPZ62

Analog Devices, Inc LFCSP-40

**ADUC841BSZ62-3**

Analog Devices, Inc QFP-52

ADSP-BF527BBCZ-5A

Analog Devices, Inc BGA-208

ADSP-BF531SBSTZ400

Analog Devices, Inc LQFP176